SOI (Silicon-On-Insulator) waferssawv cev rau cov khoom siv tshwj xeeb semiconductor featuring ib txheej ultra-thin silicon tsim rau saum ib txheej insulating oxide. Cov qauv sandwich tshwj xeeb no muab cov kev ua tau zoo txhim khu kev qha rau cov khoom siv semiconductor.

Cov Qauv Txheej Txheem:

Ntaus Txheej (Sab saum toj Silicon):

Thickness xws li los ntawm ntau nanometers mus rau micrometers, ua hauj lwm raws li cov txheej txheem rau transistor fabrication.

Thawv Oxide Layer (BOX):

Ib txheej silicon dioxide insulating txheej (0.05-15μm tuab) uas hluav taws xob cais cov txheej txheem los ntawm substrate.

Base Substrate:

Bulk silicon (100-500μm tuab) muab kev txhawb nqa txhua yam.

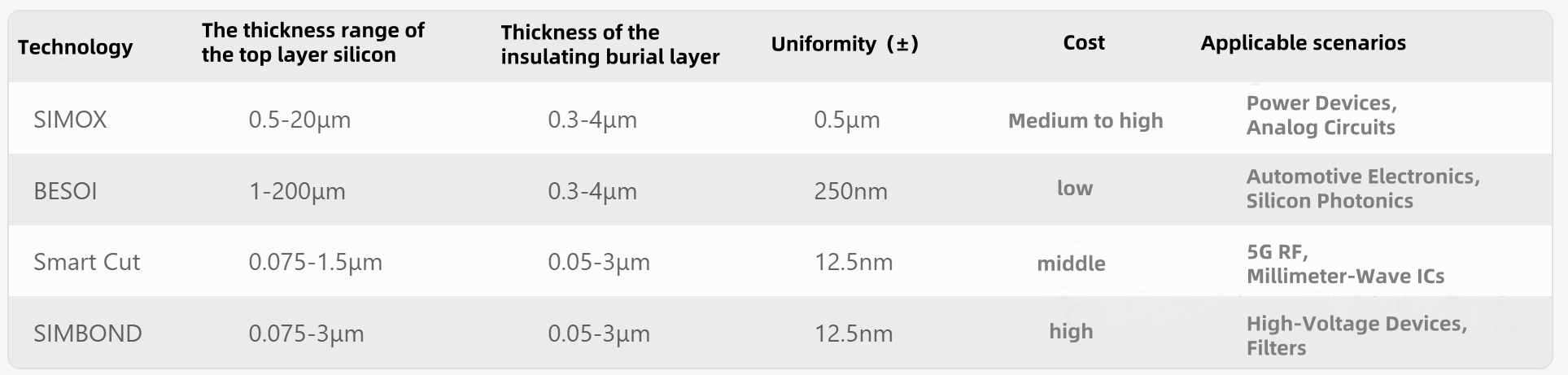

Raws li kev npaj cov txheej txheem thev naus laus zis, cov txheej txheem tseem ceeb ntawm SOI silicon wafers tuaj yeem raug cais raws li: SIMOX (oxygen txhaj tshuaj cais tshuab), BESOI (txheej txheem thev naus laus zis), thiab Ntse Txiav (ntse stripping thev naus laus zis).

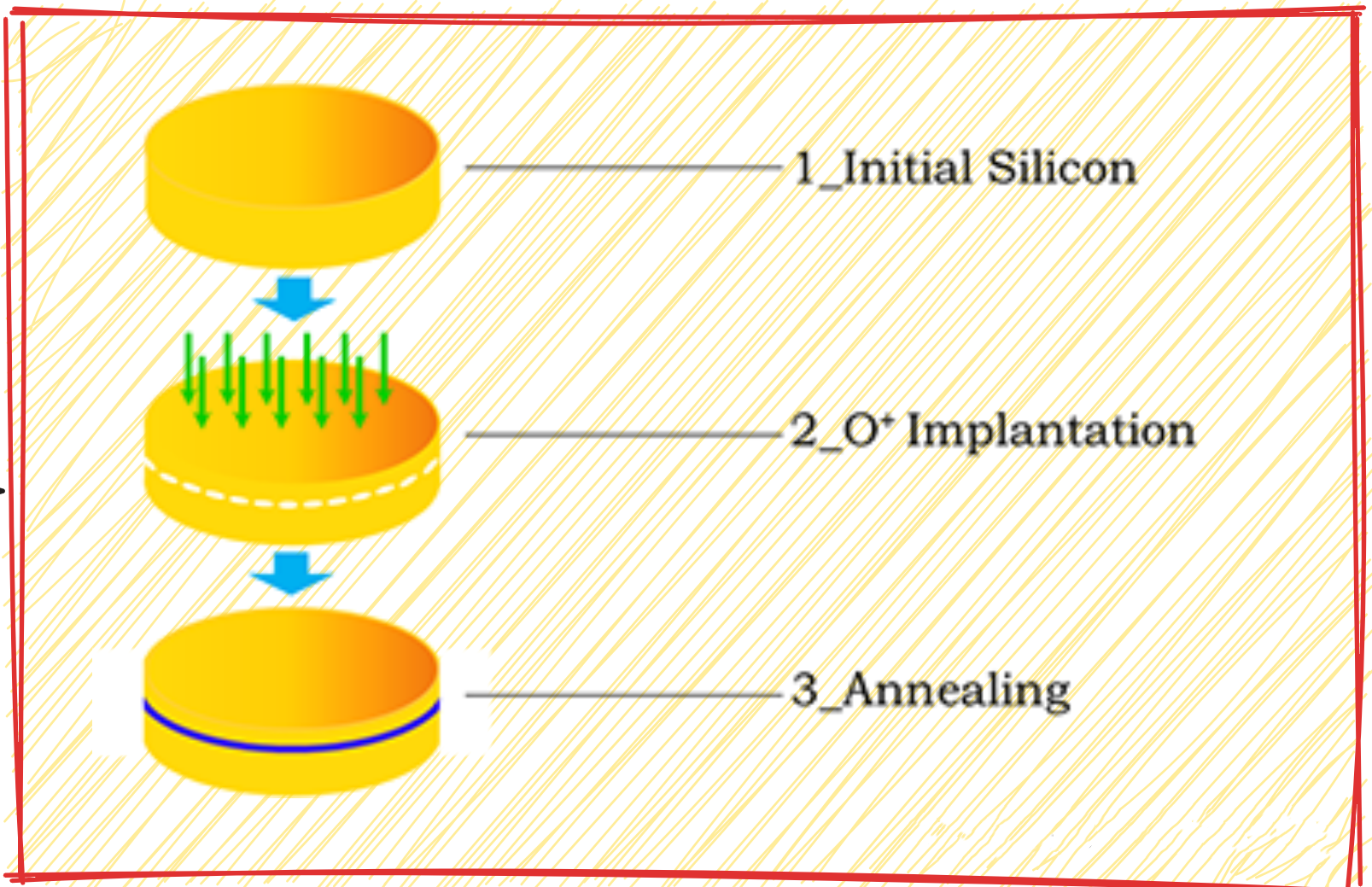

SIMOX (Oxygen injection isolation technology) yog ib qho txheej txheem uas koom nrog kev txhaj tshuaj muaj zog oxygen ions rau hauv silicon wafers los tsim ib txheej silicon dioxide embedded, uas tom qab ntawd raug kub-kub annealing los kho lattice defects. Cov tub ntxhais yog qhov ncaj qha ion oxygen txhaj rau tsim faus txheej oxygen.

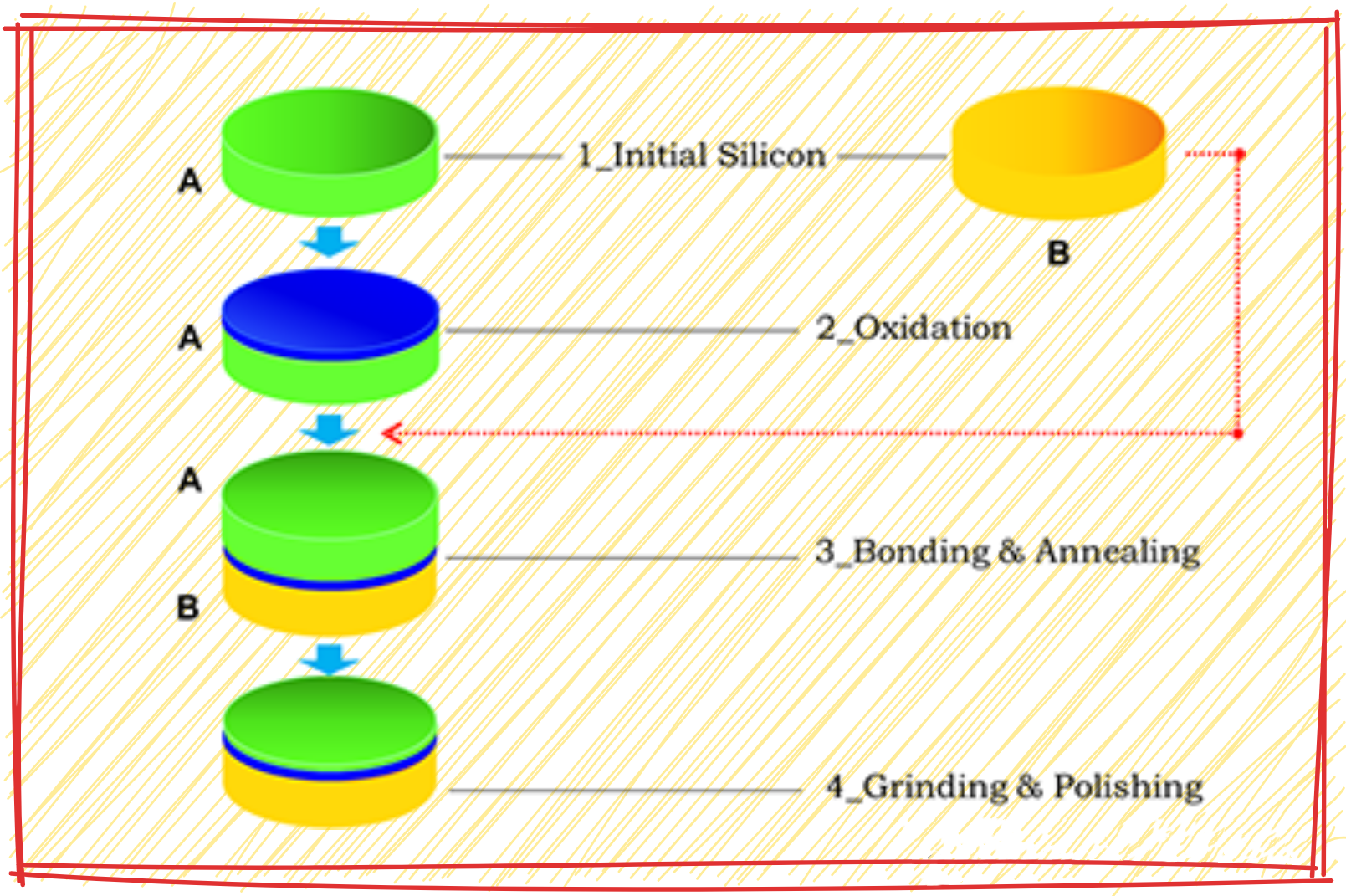

BESOI (Bonding Thinning thev naus laus zis) suav nrog kev sib koom ua ke ob lub silicon wafers thiab tom qab ntawd thinning ib qho ntawm lawv los ntawm kev sib tsoo tshuab thiab tshuaj etching los tsim ib qho qauv SOI. Lub hauv paus yog nyob rau hauv kev sib txuas thiab thinning.

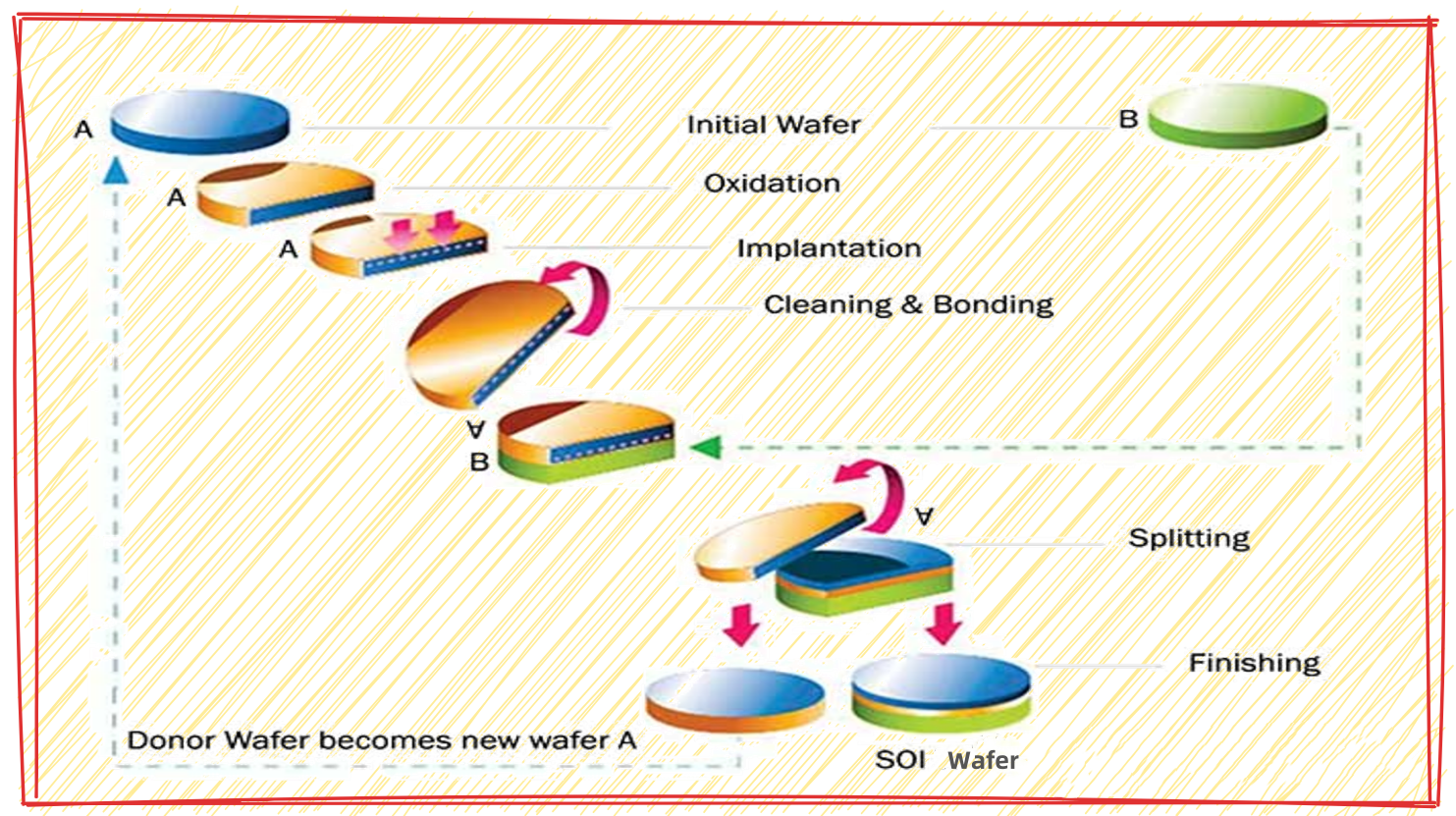

Smart Cut (Intelligent Exfoliation thev naus laus zis) tsim cov txheej txheem exfoliation los ntawm kev txhaj tshuaj hydrogen ion. Tom qab kev sib raug zoo, kev kho cua sov yog nqa tawm kom tshem tawm cov silicon wafer raws li hydrogen ion txheej, tsim cov txheej txheej silicon ultra-nyias. Lub hauv paus yog hydrogen txhaj tshuaj stripping.

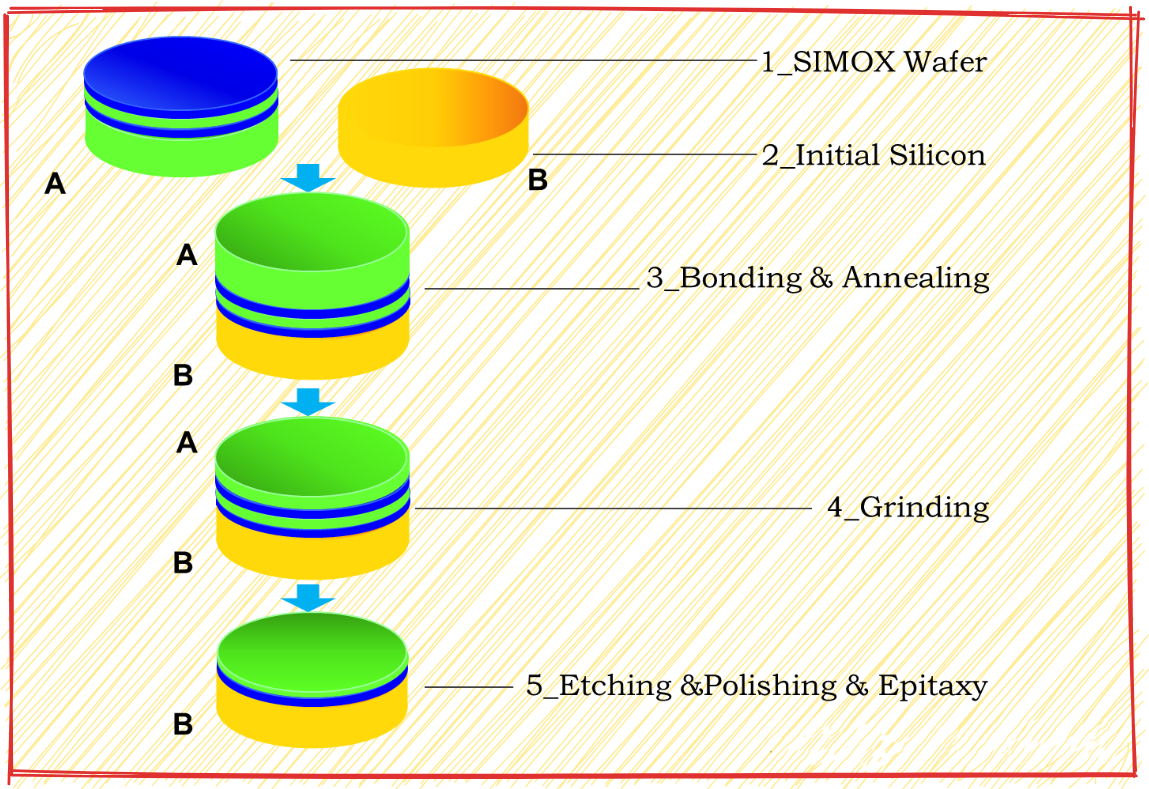

Tam sim no, muaj lwm yam thev naus laus zis hu ua SIMBOND (oxygen txhaj tshuaj tshuab), uas tau tsim los ntawm Xinao. Qhov tseeb, nws yog ib txoj hauv kev uas sib xyaw cov tshuaj tiv thaiv oxygen thiab kev sib txuas cov thev naus laus zis. Nyob rau hauv txoj kev no, cov pa oxygen txhaj yog siv los ua txheej txheej txheej txheej txheej, thiab cov txheej txheem faus cov pa yog txheej txheej thermal oxidation. Yog li ntawd, nws ib txhij txhim kho qhov tsis xws li qhov sib xws ntawm cov silicon sab saum toj thiab qhov zoo ntawm cov pa faus txheej.

SOI silicon wafers tsim los ntawm cov txheej txheem kev sib txawv muaj qhov ua tau zoo sib txawv thiab tsim nyog rau cov xwm txheej sib txawv.

Cov nram qab no yog cov ntsiab lus ntawm cov ntsiab lus zoo ntawm SOI silicon wafers, ua ke nrog lawv cov kev ua haujlwm thiab cov xwm txheej ntawm daim ntawv thov. Piv nrog rau cov tsoos bulk silicon, SOI muaj qhov zoo ntawm qhov sib npaug ntawm kev ceev thiab kev siv hluav taws xob. (PS: Kev ua tau zoo ntawm 22nm FD-SOI yog ze rau ntawm FinFET, thiab tus nqi raug txo los ntawm 30%.)

| Performance Advantage | Txoj Cai | Kev tshwm sim tshwj xeeb | Hom Daim Ntawv Thov Scenarios |

| Tsawg Parasitic Capacitance | Insulating txheej (BOX) thaiv cov nqi sib txuas ntawm cov cuab yeej thiab cov khoom siv substrate | Kev hloov ceev tau nce los ntawm 15% -30%, kev siv hluav taws xob txo los ntawm 20% -50% | 5G RF, High-frequency kev sib txuas lus chips |

| Txo cov dej ntws tam sim no | Insulating txheej suppresses to tam sim no txoj kev | Cov dej ntws tam sim no txo qis> 90%, txuas ntxiv roj teeb lub neej | Cov khoom siv IoT, Wearable electronics |

| Txhim kho Radiation Hardness | Insulating txheej blocks hluav taws xob-induced charge accumululation | Radiation kam rau ua tau zoo dua 3-5x, txo qhov kev ntxhov siab ib leeg | Spacecraft, Nuclear kev lag luam khoom siv |

| Short-Channel Effect Control | Nyias silicon txheej txo cov hluav taws xob cuam tshuam ntawm qhov ntws thiab qhov chaw | Txhim kho qhov pib voltage stability, optimized subthreshold nqes hav | Advanced node logic chips (<14nm) |

| Txhim kho Thermal Management | Insulating txheej txo cov thermal conduction coupling | 30% tsawg tshav kub tsub zuj zuj, 15-25 ° C qis kev khiav hauj lwm kub | 3D ICs, Automotive electronics |

| High-Frequency Optimization | Txo cov kab mob parasitic capacitance thiab txhim kho cov cab kuj | 20% qeeb qeeb, txhawb> 30GHz teeb liab ua | mmWave kev sib txuas lus, Satellite comm chips |

| Tsim kom muaj zog ntxiv | Tsis tas yuav tsum tau zoo doping, txhawb nqa rov qab biasing | 13% -20% tsawg dua cov txheej txheem, 40% siab dua kev sib xyaw ua ke | Mixed-signal ICs, Sensors |

| Latch-up Immunity | Insulating txheej cais cov kab mob PN junctions | Latch-up tam sim no pib nce mus rau> 100mA | Cov khoom siv hluav taws xob siab |

Raws li cov ntsiab lus, qhov zoo ntawm SOI yog: nws khiav ceev thiab muaj zog ntau dua.

Vim cov yam ntxwv ntawm kev ua tau zoo ntawm SOI, nws muaj kev siv dav hauv cov teb uas xav tau kev ua haujlwm zoo heev thiab kev siv hluav taws xob.

Raws li qhia hauv qab no, raws li kev faib ua feem ntawm daim ntawv thov teb sib xws rau SOI, nws tuaj yeem pom tias RF thiab cov khoom siv hluav taws xob suav rau feem coob ntawm SOI kev ua lag luam.

| Daim ntawv thov teb | Kev Ua Lag Luam |

| RF-SOI (Xov tooj cua zaus) | 45% |

| Lub zog SOI | 30% |

| FD-SOI (Fullly Depleted) | 15% |

| Optical TSI | 8% |

| Sensor SOI | 2% |

Nrog rau kev loj hlob ntawm kev lag luam xws li kev sib txuas lus hauv xov tooj thiab kev tsav tsheb, SOI silicon wafers kuj tseem xav kom tswj tau qee qhov kev loj hlob.

XKH, ua tus thawj coj tsim kho tshiab hauv Silicon-On-Insulator (SOI) wafer thev naus laus zis, xa cov kev daws teeb meem SOI los ntawm R&D mus rau ntim ntau lawm siv cov txheej txheem kev lag luam ua lag luam. Peb cov ntaub ntawv tiav suav nrog 200mm / 300mm SOI wafers hla RF-SOI, Lub Hwj Chim-SOI thiab FD-SOI variants, nrog kev tswj xyuas nruj kom ntseeg tau qhov kev ua tau zoo sib xws (thickness uniformity li ± 1.5%). Peb muab cov kev daws teeb meem customized nrog faus oxide (BOX) txheej thickness xws li 50nm mus rau 1.5μm thiab ntau yam resistivity specifications kom tau raws li cov kev cai tshwj xeeb. Leveraging 15 xyoo ntawm kev txawj ntse thiab ib tug robust thoob ntiaj teb cov saw hlau, peb ntseeg siab muab high-zoo SOI substrate cov ntaub ntawv rau saum-tier semiconductor manufacturers thoob ntiaj teb, ua rau kev txiav-ntug nti nrhav nyob rau hauv 5G kev sib txuas lus, automotive electronics, thiab artificial txawj ntse daim ntaub ntawv.

Lub sij hawm xa tuaj: Plaub Hlis-24-2025