4 nti SiC Wafers 6H Semi-Insulating SiC Substrates prime, kev tshawb fawb, thiab qib dummy

Khoom Specification

| Qib | Zero MPD Qhuav Qib (Z Qib) | Standard Qhuav Qib (P Qib) | Qib Dummy (D qib) | ||||||||

| Txoj kab uas hla | 99.5mm ~ 100.0 hli | ||||||||||

| 4 H-SI | 500 μm ± 20 μm | 500 μm ± 25 μm | |||||||||

| Wafer Orientation |

Tawm axis: 4.0 ° rau < 1120 > ± 0.5 ° rau 4H-N, Ntawm axis: <0001> ± 0.5 ° rau 4H-SI | ||||||||||

| 4 H-SI | ≤1cm-2 | ≤ 5 cm-2 | ≤ 15 cm-2 | ||||||||

| 4 H-SI | ≥1E9 Ω·cm | ≥1E5 Ω·cm | |||||||||

| Thawj Txoj Kev Ncaj Ncees | {10-10} ± 5.0° | ||||||||||

| Qhov Loj Loj Loj | 32.5 hli ± 2.0 hli | ||||||||||

| Secondary Flat Length | 18.0mm ± 2.0 hli | ||||||||||

| Secondary Flat Orientation | Silicon lub ntsej muag: 90 ° CW. los ntawm Prime tiaj tus ± 5.0 ° | ||||||||||

| Ntug Exclusion | 3 hli | ||||||||||

| LTV/TTV/How/Warp | ≤ 3 μm / ≤ 5 μm / ≤ 15 μm / ≤ 30 μm | ≤ 10 μm / ≤ 15 μm / ≤ 25 μm / ≤ 40 μm | |||||||||

| Roughness | C ntsej muag | Polish | Ra≤1nm | ||||||||

| Si face | CMP | Ra≤0.2nm | Ra≤0.5nm | ||||||||

| Ntug Cracks Los ntawm High Intensity Light | Tsis muaj | Qhov ntev ≤ 10 mm, ib leeg ntev ≤ 2 mm | |||||||||

| Hex Phaj Los Ntawm Lub Teeb Siab Siab | Thaj tsam ≤ 0.05% | Qhov loj me ≤0.1% | |||||||||

| Polytype Areas Los Ntawm Lub Teeb Siab Siab | Tsis muaj | Thaj tsam ≤ 3% | |||||||||

| Visual Carbon suav nrog | Thaj tsam ≤ 0.05% | Qhov loj me ≤ 3% | |||||||||

| Silicon Surface Scratches Los ntawm High Intensity Light | Tsis muaj | Qhov ntev ntawm qhov ntsuas ≤1 * wafer txoj kab uas hla | |||||||||

| Ntug Chips Siab Los Ntawm Kev Siv Lub Teeb | Tsis muaj kev tso cai ≥0.2 hli dav thiab qhov tob | 5 tso cai, ≤1mm txhua | |||||||||

| Silicon Surface Contamination Los Ntawm Kev Siv Siab | Tsis muaj | ||||||||||

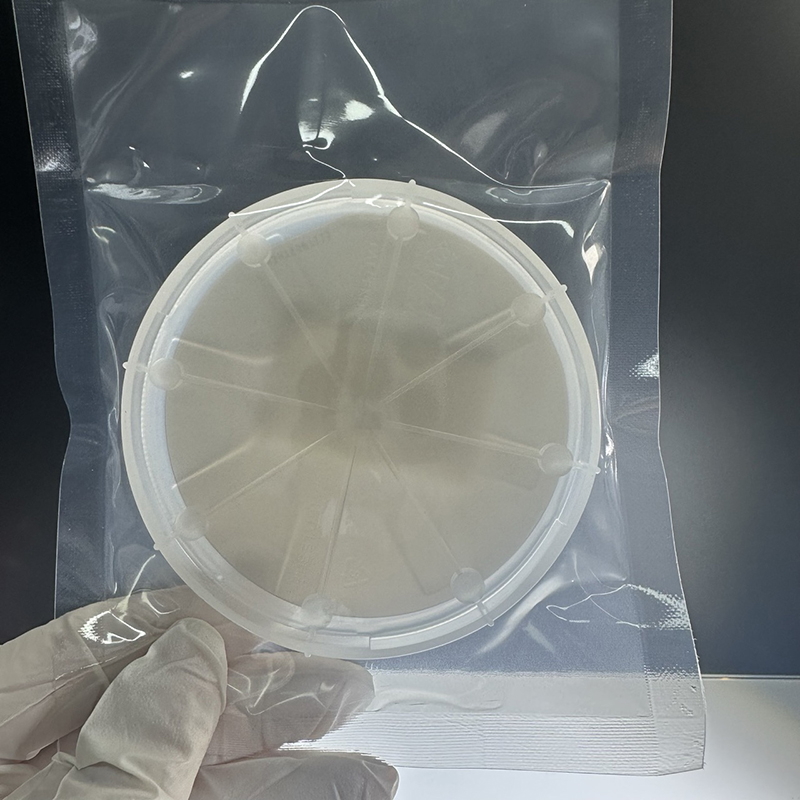

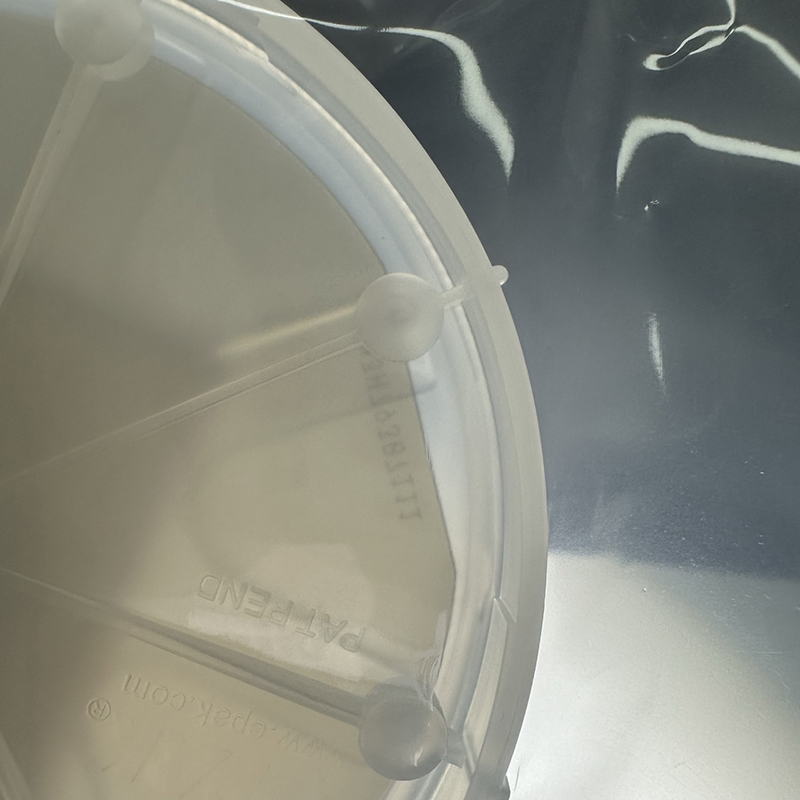

| Ntim | Multi-wafer Cassette lossis Ib Lub Thawv Wafer | ||||||||||

Daim duab qhia ntxaws

Yam khoom

Sau koj cov lus ntawm no thiab xa tuaj rau peb