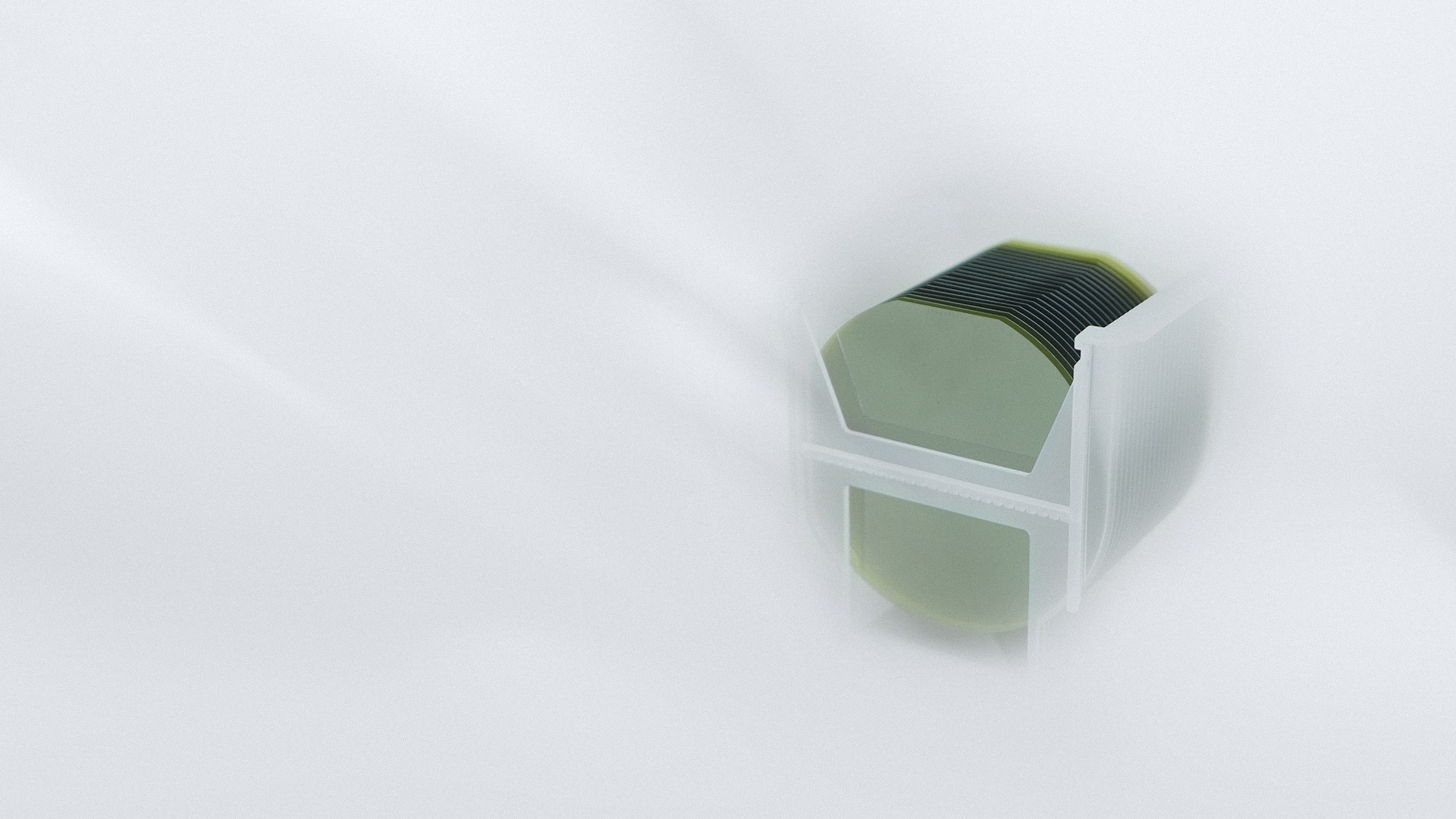

4H-N HPSI SiC wafer 6H-N 6H-P 3C-N SiC Epitaxial wafer rau MOS lossis SBD

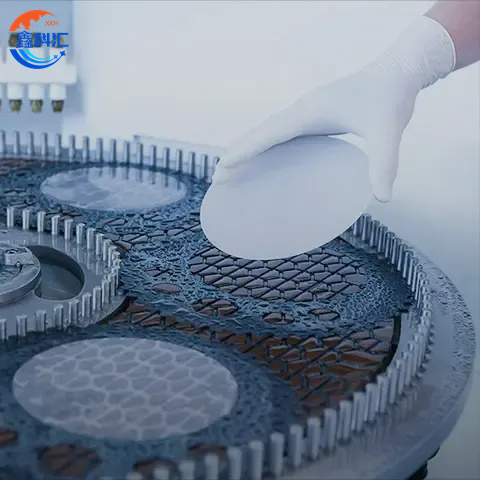

SiC Substrate SiC Epi-wafer Luv Luv

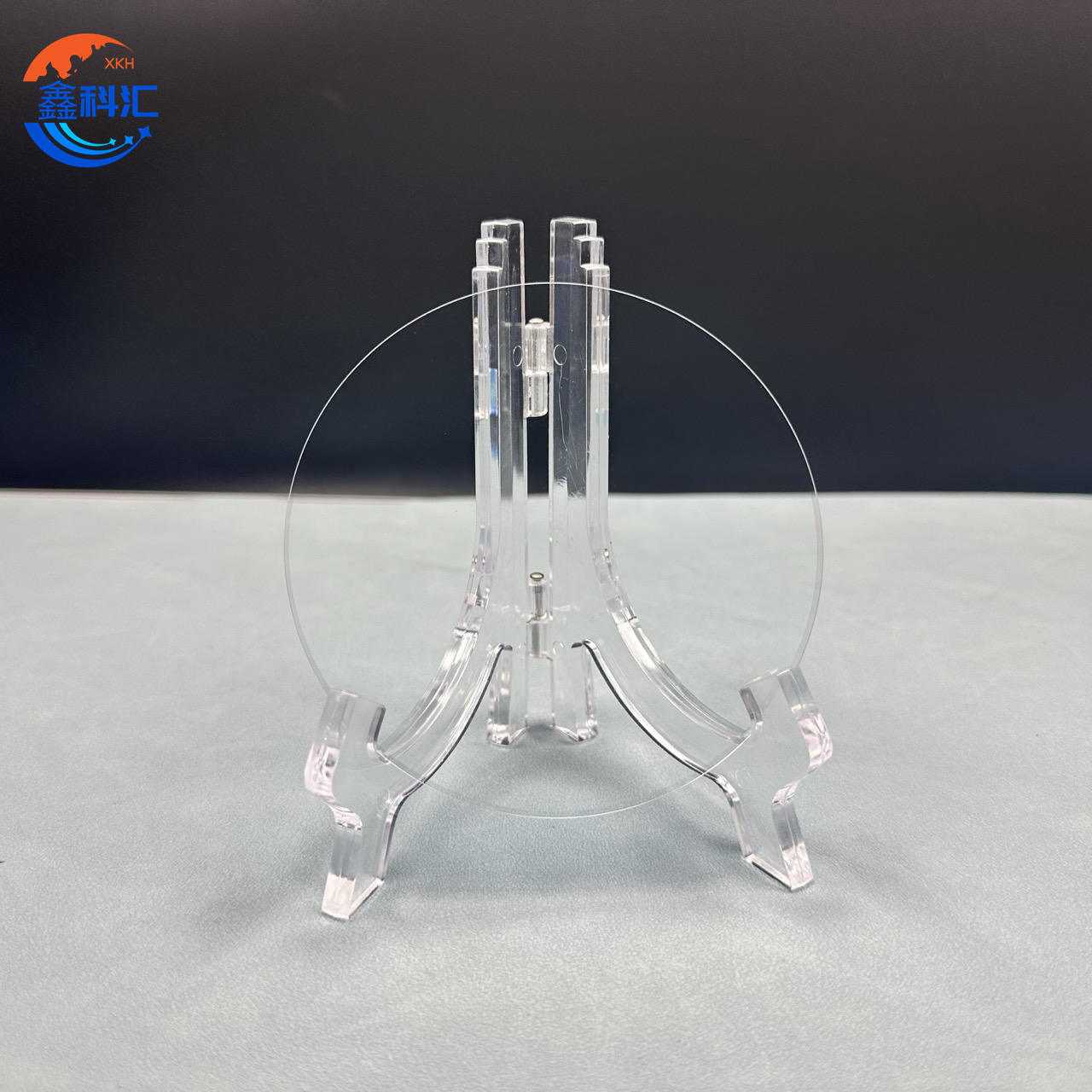

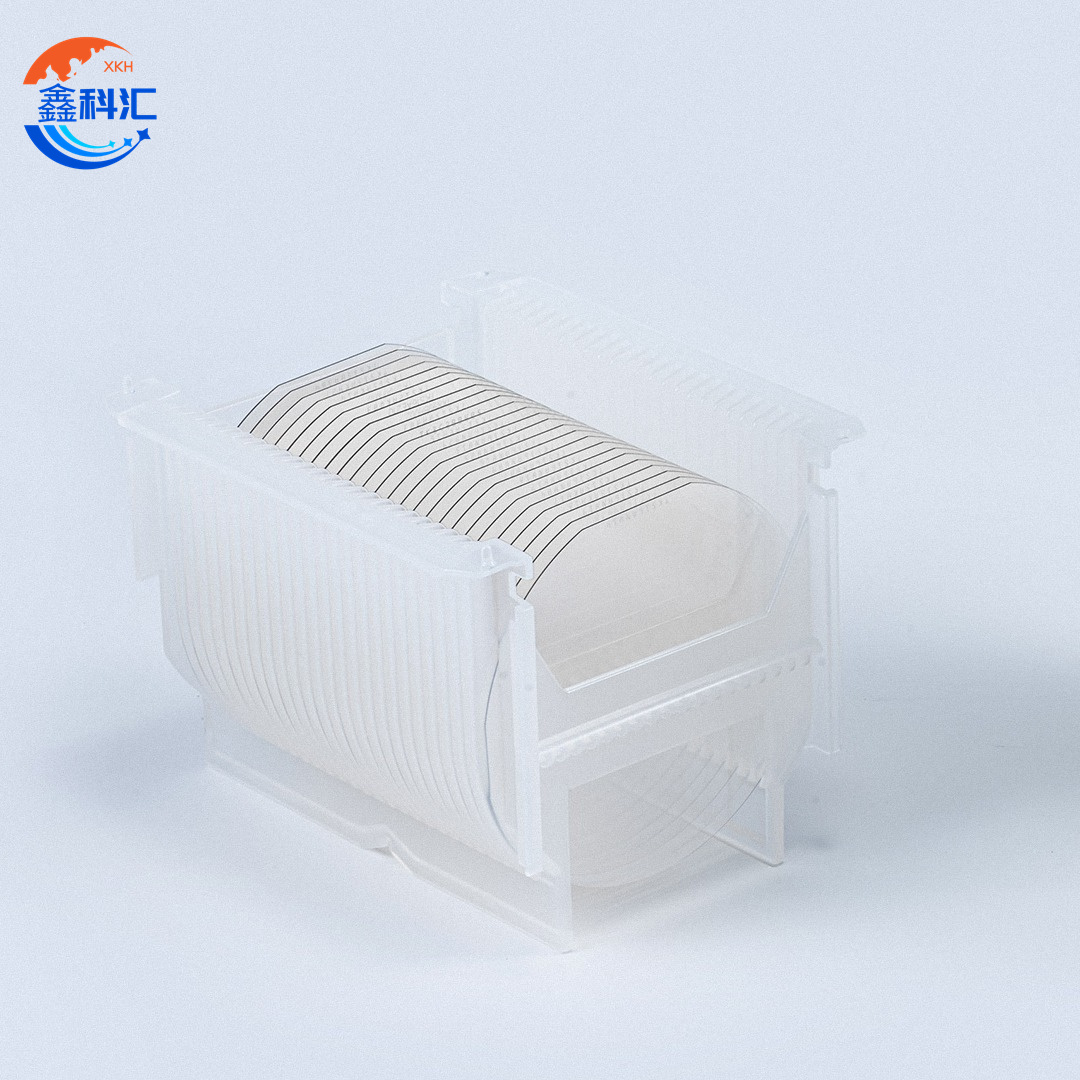

Peb muab cov khoom siv SiC zoo thiab sic wafers hauv ntau hom polytypes thiab doping profiles—xws li 4H-N (n-hom conductive), 4H-P (p-hom conductive), 4H-HPSI (high-purity semi-insulating), thiab 6H-P (p-hom conductive)—hauv txoj kab uas hla los ntawm 4″, 6″, thiab 8″ txog 12″. Dhau ntawm cov substrates liab qab, peb cov kev pabcuam loj hlob epi wafer muaj nqis ntxiv xa cov epitaxial (epi) wafers nrog cov tuab tswj tau nruj (1–20 µm), cov doping concentration, thiab cov qhov tsis xws luag.

Txhua lub sic wafer thiab epi wafer raug tshuaj xyuas nruj hauv kab (micropipe density <0.1 cm⁻², surface roughness Ra <0.2 nm) thiab tag nrho cov yam ntxwv hluav taws xob (CV, resistivity mapping) kom ntseeg tau tias muaj kev sib xws thiab kev ua tau zoo. Txawm siv rau cov khoom siv hluav taws xob fais fab, cov amplifiers RF siab, lossis cov khoom siv optoelectronic (LEDs, photodetectors), peb cov khoom SiC substrate thiab epi wafer xa cov kev ntseeg tau, thermal stability, thiab lub zog tawg uas xav tau los ntawm cov ntawv thov niaj hnub no.

Cov yam ntxwv thiab daim ntawv thov ntawm SiC Substrate 4H-N hom

-

4H-N SiC substrate Polytype (Hexagonal) Qauv

Qhov bandgap dav ntawm ~3.26 eV ua kom muaj kev ua haujlwm hluav taws xob ruaj khov thiab kev ua haujlwm thermal robustness nyob rau hauv qhov kub thiab txias siab thiab cov xwm txheej hluav taws xob siab.

-

SiC substrateN-Hom Doping

Kev tswj hwm cov nitrogen doping meej ua rau muaj cov carrier concentration ntawm 1 × 10¹⁶ txog 1 × 10¹⁹ cm⁻³ thiab cov electron mobility hauv chav sov txog li ~ 900 cm² / V · s, txo qis kev poob ntawm conduction.

-

SiC substrateKev Tiv Thaiv Dav Dav & Kev Sib Xws

Muaj qhov ntau ntawm resistivity ntawm 0.01–10 Ω·cm thiab wafer thicknesses ntawm 350–650 µm nrog ± 5% kev kam rau siab hauv ob qho tib si doping thiab thickness - zoo tagnrho rau kev tsim khoom siv hluav taws xob siab.

-

SiC substrateQhov Ceev Tsis Zoo Ultra-Low

Qhov ceev ntawm cov kav dej me me < 0.1 cm⁻² thiab qhov ceev ntawm qhov tawg ntawm lub basal-plane < 500 cm⁻², ua rau muaj > 99% ntawm cov khoom siv thiab kev ua kom zoo dua ntawm cov siv lead ua.

- SiC substrateKev Ua Haujlwm Thermal Zoo Tshaj Plaws

Kev ua kom sov tau txog li ~370 W/m·K ua rau kev tshem tawm cua sov zoo, ua rau kev ntseeg siab ntawm cov khoom siv thiab lub zog ceev.

-

SiC substrateCov Ntawv Thov

SiC MOSFETs, Schottky diodes, cov modules fais fab thiab RF cov khoom siv rau cov tsav tsheb fais fab, cov inverters hnub ci, cov tsav tsheb lag luam, cov tshuab traction, thiab lwm yam kev lag luam fais fab-electronics uas xav tau ntau.

6 nti 4H-N hom SiC wafer cov lus qhia tshwj xeeb | ||

| Vaj tse | Qib Tsim Khoom Xoom MPD (Qib Z) | Qib Dummy (Qib D) |

| Qib | Qib Tsim Khoom Xoom MPD (Qib Z) | Qib Dummy (Qib D) |

| Txoj kab uas hla | 149.5 hli - 150.0 hli | 149.5 hli - 150.0 hli |

| Poly-hom | 4H | 4H |

| Qhov tuab | 350 µm ± 15 µm | 350 µm ± 25 µm |

| Kev Taw Qhia Wafer | Tawm ntawm txoj kab: 4.0° mus rau <1120> ± 0.5° | Tawm ntawm txoj kab: 4.0° mus rau <1120> ± 0.5° |

| Qhov Ceev ntawm Micropipe | ≤ 0.2 cm² | ≤ 15 cm² |

| Kev tiv taus | 0.015 - 0.024 Ω·cm | 0.015 - 0.028 Ω·cm |

| Kev Taw Qhia Tiaj Tus Thawj Coj | [10-10] ± 50° | [10-10] ± 50° |

| Qhov Ntev Tiaj Tus Thawj | 475 hli ± 2.0 hli | 475 hli ± 2.0 hli |

| Kev Tshem Tawm Ntug | 3 hli | 3 hli |

| LTV/TIV / Bow / Warp | ≤ 2.5 µm / ≤ 6 µm / ≤ 25 µm / ≤ 35 µm | ≤ 5 µm / ≤ 15 µm / ≤ 40 µm / ≤ 60 µm |

| Kev ntxhib | Polish Ra ≤ 1 nm | Polish Ra ≤ 1 nm |

| CMP Ra | ≤ 0.2 nm | ≤ 0.5 nm |

| Cov Ntxaij Ntug Los Ntawm Lub Teeb Ci Siab | Qhov ntev tag nrho ≤ 20 hli ib qho ntev ≤ 2 hli | Qhov ntev tag nrho ≤ 20 hli ib qho ntev ≤ 2 hli |

| Hex Phaj Los Ntawm Lub Teeb Ci Siab | Thaj chaw sib sau ua ke ≤ 0.05% | Thaj chaw sib sau ua ke ≤ 0.1% |

| Cov Cheeb Tsam Polytype Los Ntawm Lub Teeb Ci Siab | Thaj chaw sib sau ua ke ≤ 0.05% | Thaj chaw sib sau ua ke ≤ 3% |

| Cov pa roj carbon uas pom tau | Thaj chaw sib sau ua ke ≤ 0.05% | Thaj chaw sib sau ua ke ≤ 5% |

| Cov khawb ntawm cov nplaim silicon los ntawm lub teeb ci ntsa iab | Qhov ntev tag nrho ≤ 1 lub wafer txoj kab uas hla | |

| Ntug Chips Los Ntawm Lub Teeb Ci Siab | Tsis pub muaj ≥ 0.2 hli dav thiab tob | 7 tso cai, ≤ 1 hli txhua |

| Kev Sib Tsoo Ntawm Cov Ntsia Hlau | < 500 cm³ | < 500 cm³ |

| Kev Ua Rau Silicon Nto Los Ntawm Lub Teeb Ci Siab | ||

| Ntim Khoom | Multi-wafer Cassette Los Yog Ib Lub Thawv Wafer | Multi-wafer Cassette Los Yog Ib Lub Thawv Wafer |

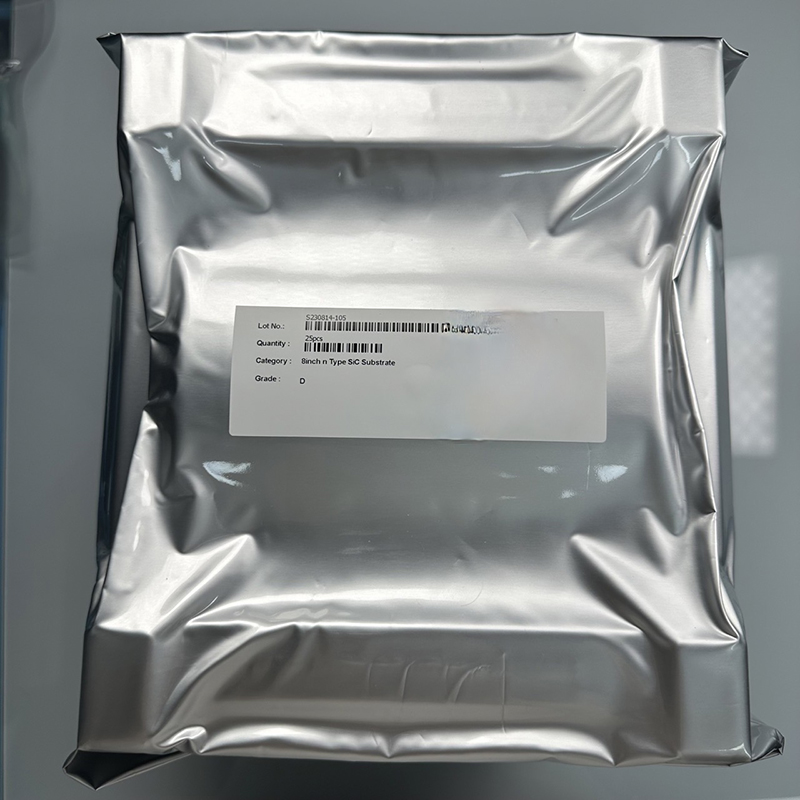

8 nti 4H-N hom SiC wafer cov lus qhia tshwj xeeb | ||

| Vaj tse | Qib Tsim Khoom Xoom MPD (Qib Z) | Qib Dummy (Qib D) |

| Qib | Qib Tsim Khoom Xoom MPD (Qib Z) | Qib Dummy (Qib D) |

| Txoj kab uas hla | 199.5 hli - 200.0 hli | 199.5 hli - 200.0 hli |

| Poly-hom | 4H | 4H |

| Qhov tuab | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Kev Taw Qhia Wafer | 4.0° mus rau <110> ± 0.5° | 4.0° mus rau <110> ± 0.5° |

| Qhov Ceev ntawm Micropipe | ≤ 0.2 cm² | ≤ 5 cm² |

| Kev tiv taus | 0.015 - 0.025 Ω·cm | 0.015 - 0.028 Ω·cm |

| Kev Taw Qhia Zoo | ||

| Kev Tshem Tawm Ntug | 3 hli | 3 hli |

| LTV/TIV / Bow / Warp | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 70 µm | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 100 µm |

| Kev ntxhib | Polish Ra ≤ 1 nm | Polish Ra ≤ 1 nm |

| CMP Ra | ≤ 0.2 nm | ≤ 0.5 nm |

| Cov Ntxaij Ntug Los Ntawm Lub Teeb Ci Siab | Qhov ntev tag nrho ≤ 20 hli ib qho ntev ≤ 2 hli | Qhov ntev tag nrho ≤ 20 hli ib qho ntev ≤ 2 hli |

| Hex Phaj Los Ntawm Lub Teeb Ci Siab | Thaj chaw sib sau ua ke ≤ 0.05% | Thaj chaw sib sau ua ke ≤ 0.1% |

| Cov Cheeb Tsam Polytype Los Ntawm Lub Teeb Ci Siab | Thaj chaw sib sau ua ke ≤ 0.05% | Thaj chaw sib sau ua ke ≤ 3% |

| Cov pa roj carbon uas pom tau | Thaj chaw sib sau ua ke ≤ 0.05% | Thaj chaw sib sau ua ke ≤ 5% |

| Cov khawb ntawm cov nplaim silicon los ntawm lub teeb ci ntsa iab | Qhov ntev tag nrho ≤ 1 lub wafer txoj kab uas hla | |

| Ntug Chips Los Ntawm Lub Teeb Ci Siab | Tsis pub muaj ≥ 0.2 hli dav thiab tob | 7 tso cai, ≤ 1 hli txhua |

| Kev Sib Tsoo Ntawm Cov Ntsia Hlau | < 500 cm³ | < 500 cm³ |

| Kev Ua Rau Silicon Nto Los Ntawm Lub Teeb Ci Siab | ||

| Ntim Khoom | Multi-wafer Cassette Los Yog Ib Lub Thawv Wafer | Multi-wafer Cassette Los Yog Ib Lub Thawv Wafer |

4H-SiC yog ib yam khoom siv ua tau zoo siv rau cov khoom siv hluav taws xob, cov khoom siv RF, thiab cov ntawv thov kub siab. Tus "4H" txhais tau tias yog cov qauv siv lead ua, uas yog hexagonal, thiab tus "N" txhais tau tias yog hom doping siv los ua kom cov khoom siv ua tau zoo dua.

Lub4H-SiChom no feem ntau siv rau:

Cov Khoom Siv Hluav Taws Xob:Siv rau hauv cov khoom siv xws li diodes, MOSFETs, thiab IGBTs rau cov tsheb fais fab, cov tshuab kev lag luam, thiab cov tshuab hluav taws xob rov ua dua tshiab.

5G Tshuab:Nrog 5G qhov kev thov rau cov khoom siv zaus siab thiab ua haujlwm tau zoo, SiC lub peev xwm los tswj cov hluav taws xob siab thiab ua haujlwm ntawm qhov kub siab ua rau nws zoo tagnrho rau cov amplifiers fais fab chaw nres tsheb thiab cov khoom siv RF.

Cov Txheej Txheem Fais Fab Hnub Ci:SiC cov khoom siv hluav taws xob zoo heev yog qhov zoo tagnrho rau photovoltaic (hnub ci zog) inverters thiab converters.

Cov Tsheb Fais Fab (EVs):SiC siv dav hauv EV powertrains rau kev hloov pauv hluav taws xob zoo dua, txo qis cua sov, thiab muaj zog ntau dua.

SiC Substrate 4H Semi-Insulating hom cov yam ntxwv thiab daim ntawv thov

Cov Khoom:

-

Cov txheej txheem tswj kev ceev tsis muaj micropipe: Xyuas kom tsis muaj cov kav dej me me, txhim kho qhov zoo ntawm cov khoom siv.

-

Cov txheej txheem tswj hwm monocrystalline: Lav ib qho qauv siv lead ua ke rau cov khoom siv txhim kho.

-

Cov txheej txheem tswj kev suav nrog: Txo qhov muaj cov khoom tsis huv los yog cov khoom sib xyaw, ua kom cov khoom siv huv si.

-

Cov txheej txheem tswj kev tiv thaiv: Tso cai rau kev tswj hwm qhov hluav taws xob resistivity, uas yog qhov tseem ceeb rau kev ua haujlwm ntawm lub cuab yeej.

-

Kev tswj thiab tswj kev ua qias tuaj: Tswj thiab txwv tsis pub muaj cov khoom tsis huv los tswj kev ua kom cov substrate ruaj khov.

-

Cov txheej txheem tswj qhov dav ntawm cov kauj ruam substrate: Muab kev tswj hwm qhov dav ntawm cov kauj ruam kom raug, ua kom muaj kev sib xws thoob plaws hauv cov substrate

6Inch 4H-semi SiC substrate specification | ||

| Vaj tse | Qib Tsim Khoom Xoom MPD (Qib Z) | Qib Dummy (Qib D) |

| Txoj kab uas hla (hli) | 145 hli - 150 hli | 145 hli - 150 hli |

| Poly-hom | 4H | 4H |

| Thickness (um) | 500 ± 15 | 500 ± 25 |

| Kev Taw Qhia Wafer | Nyob rau ntawm axis: ± 0.0001 ° | Ntawm axis: ±0.05° |

| Qhov Ceev ntawm Micropipe | ≤ 15 cm-2 | ≤ 15 cm-2 |

| Kev tiv thaiv (Ωcm) | ≥ 10E3 | ≥ 10E3 |

| Kev Taw Qhia Tiaj Tus Thawj Coj | (0-10)° ± 5.0° | (10-10)° ± 5.0° |

| Qhov Ntev Tiaj Tus Thawj | Qhov Notch | Qhov Notch |

| Kev Tshem Tawm Ntug (hli) | ≤ 2.5 µm / ≤ 15 µm | ≤ 5.5 µm / ≤ 35 µm |

| LTV / Bowl / Warp | ≤ 3 µm | ≤ 3 µm |

| Kev ntxhib | Polish Ra ≤ 1.5 µm | Polish Ra ≤ 1.5 µm |

| Ntug Chips Los Ntawm Lub Teeb Ci Siab | ≤ 20 µm | ≤ 60 µm |

| Cov Phaj Kub Los Ntawm Lub Teeb Ci Siab | Tag nrho ≤ 0.05% | Tag nrho ≤ 3% |

| Cov Cheeb Tsam Polytype Los Ntawm Lub Teeb Ci Siab | Cov Pa roj carbon uas pom tau ≤ 0.05% | Tag nrho ≤ 3% |

| Cov khawb ntawm cov nplaim silicon los ntawm lub teeb ci ntsa iab | ≤ 0.05% | Tag nrho ≤ 4% |

| Cov Chips Ntug Los Ntawm Lub Teeb Ci Siab (Qhov Loj) | Tsis Pub > 02 hli Dav thiab Qhov Tob | Tsis Pub > 02 hli Dav thiab Qhov Tob |

| Kev Pab Txhawb Nqa Kev Nthuav Dav | ≤ 500 µm | ≤ 500 µm |

| Kev Ua Rau Silicon Nto Los Ntawm Lub Teeb Ci Siab | ≤ 1 x 10^5 | ≤ 1 x 10^5 |

| Ntim Khoom | Multi-wafer Cassette los yog Single Wafer Thawv | Multi-wafer Cassette los yog Single Wafer Thawv |

Cov Lus Qhia Txog 4-Nti 4H-Semi Insulating SiC Substrate

| Cov Qauv | Qib Tsim Khoom Xoom MPD (Qib Z) | Qib Dummy (Qib D) |

|---|---|---|

| Cov Khoom Siv Lub Cev | ||

| Txoj kab uas hla | 99.5 hli - 100.0 hli | 99.5 hli - 100.0 hli |

| Poly-hom | 4H | 4H |

| Qhov tuab | 500 μm ± 15 μm | 500 μm ± 25 μm |

| Kev Taw Qhia Wafer | Nyob rau ntawm axis: <600h> 0.5° | Nyob rau ntawm axis: <000h> 0.5 ° |

| Cov Khoom Siv Hluav Taws Xob | ||

| Qhov Ceev ntawm Cov Kav Dej Me Me (MPD) | ≤1 cm⁻² | ≤15 cm⁻² |

| Kev tiv taus | ≥150 Ω·cm | ≥1.5 Ω·cm |

| Kev kam rau siab geometric | ||

| Kev Taw Qhia Tiaj Tus Thawj Coj | (0x10) ± 5.0° | (0x10) ± 5.0° |

| Qhov Ntev Tiaj Tus Thawj | 52.5 hli ± 2.0 hli | 52.5 hli ± 2.0 hli |

| Qhov Ntev Thib Ob | 18.0 hli ± 2.0 hli | 18.0 hli ± 2.0 hli |

| Kev Taw Qhia Qib Thib Ob | 90° CW ntawm Prime tiaj tus ± 5.0° (Si ntsej muag rau saum) | 90° CW ntawm Prime tiaj tus ± 5.0° (Si ntsej muag rau saum) |

| Kev Tshem Tawm Ntug | 3 hli | 3 hli |

| LTV / TTV / Bow / Warp | ≤2.5 μm / ≤5 μm / ≤15 μm / ≤30 μm | ≤10μm / ≤15μm / ≤25μm / ≤40μm |

| Qhov Zoo Ntawm Qhov Chaw | ||

| Qhov Roughness ntawm qhov chaw (Polish Ra) | ≤1 nm | ≤1 nm |

| Qhov Roughness ntawm Qhov Chaw (CMP Ra) | ≤0.2 nm | ≤0.2 nm |

| Cov Ntxaij Ntug (Lub Teeb Ci Muaj Zog) | Tsis pub | Qhov ntev sib sau ua ke ≥10 hli, ib qho tawg ≤2 hli |

| Cov Teeb Meem Phaj Hexagonal | ≤0.05% thaj chaw sib sau ua ke | ≤0.1% thaj chaw sib sau ua ke |

| Cov Cheeb Tsam suav nrog Polytype | Tsis pub | ≤1% thaj chaw sib sau ua ke |

| Cov pa roj carbon uas pom tau | ≤0.05% thaj chaw sib sau ua ke | ≤1% thaj chaw sib sau ua ke |

| Cov khawb ntawm qhov chaw silicon | Tsis pub | ≤1 wafer txoj kab uas hla cumulative ntev |

| Cov Chips Ntug | Tsis pub muaj (≥0.2 hli dav/qhov tob) | ≤5 daim (txhua ≤1 hli) |

| Kev Ua Phem Rau Qhov Chaw Silicon | Tsis tau teev tseg | Tsis tau teev tseg |

| Ntim Khoom | ||

| Ntim Khoom | Lub thawv ntim ntau lub wafer los yog lub thawv ntim ib lub wafer | Cov cassette ntau lub wafer los yog |

Daim Ntawv Thov:

LubSiC 4H Semi-Insulating substratesfeem ntau yog siv rau hauv cov khoom siv hluav taws xob muaj zog thiab siab zaus, tshwj xeeb tshaj yog nyob rau hauvRF tebCov substrates no tseem ceeb heev rau ntau yam kev siv xws licov txheej txheem sib txuas lus microwave, phased array radar, thiabcov cuab yeej hluav taws xob wirelessLawv cov thermal conductivity siab thiab cov yam ntxwv hluav taws xob zoo heev ua rau lawv zoo tagnrho rau cov ntawv thov uas xav tau ntau hauv cov khoom siv hluav taws xob thiab cov kab ke sib txuas lus.

SiC epi wafer 4H-N hom khoom thiab daim ntawv thov

SiC 4H-N Hom Epi Wafer Cov Khoom thiab Daim Ntawv Thov

Cov Khoom ntawm SiC 4H-N Hom Epi Wafer:

Cov Khoom Siv Muaj pes tsawg leeg:

SiC (Silicon Carbide): Paub txog nws qhov kev tawv zoo heev, kev ua kom sov siab, thiab cov khoom siv hluav taws xob zoo heev, SiC yog qhov zoo tagnrho rau cov khoom siv hluav taws xob ua haujlwm siab.

4H-SiC Polytype: Lub 4H-SiC polytype paub txog nws qhov kev ua haujlwm siab thiab kev ruaj khov hauv kev siv hluav taws xob.

N-hom DopingN-hom doping (doped nrog nitrogen) muab kev txav mus los zoo heev ntawm cov hluav taws xob, ua rau SiC haum rau kev siv zaus siab thiab lub zog siab.

Kev Ua Haujlwm Thermal Siab:

SiC wafers muaj cov thermal conductivity zoo dua, feem ntau yog txij li120–200 W/m·K, uas tso cai rau lawv kom tswj tau cua sov hauv cov khoom siv hluav taws xob siab xws li transistors thiab diodes.

Dav Bandgap:

Nrog ib qho bandgap ntawm3.26 eV, 4H-SiC tuaj yeem ua haujlwm ntawm qhov hluav taws xob siab dua, zaus, thiab kub dua piv rau cov khoom siv silicon ib txwm muaj, ua rau nws zoo tagnrho rau kev siv ua haujlwm siab, kev ua haujlwm siab.

Cov Khoom Siv Hluav Taws Xob:

SiC lub zog hluav taws xob siab thiab kev coj ua ua rau nws zoo tagnrho rauhluav taws xob, muab kev hloov pauv ceev thiab muaj peev xwm tswj tau tam sim no thiab voltage siab, ua rau muaj kev tswj hwm hluav taws xob zoo dua.

Kev Tiv Thaiv Tshuab thiab Tshuaj Lom Zem:

SiC yog ib qho ntawm cov ntaub ntawv nyuaj tshaj plaws, thib ob tsuas yog pob zeb diamond, thiab nws tiv taus oxidation thiab corrosion heev, ua rau nws ruaj khov nyob rau hauv ib puag ncig hnyav.

Cov ntawv thov ntawm SiC 4H-N Hom Epi Wafer:

Cov Khoom Siv Hluav Taws Xob:

SiC 4H-N hom epi wafers siv dav hauvMOSFETs fais fab, Cov IGBT, thiabcov dioderaukev hloov pauv fais fabhauv cov kab ke xws licov inverters hnub ci, tsheb fais fab, thiabcov txheej txheem khaws cia hluav taws xob, muab kev ua tau zoo dua thiab kev siv hluav taws xob zoo dua.

Cov Tsheb Fais Fab (EVs):

In cov tsheb fais fab, cov tswj lub cev muaj zog, thiabchaw them nqi, SiC wafers pab ua kom lub roj teeb ua haujlwm tau zoo dua, them sai dua, thiab txhim kho kev ua haujlwm hluav taws xob tag nrho vim lawv muaj peev xwm tswj tau lub zog siab thiab kub.

Cov Txheej Txheem Fais Fab Rov Ua Dua Tshiab:

Cov Inverters Hnub CiSiC wafers siv rau hauvcov tshuab hluav taws xob hnub cirau kev hloov DC fais fab los ntawm cov vaj huam sib luag hnub ci mus rau AC, ua kom tag nrho cov txheej txheem ua haujlwm tau zoo thiab ua tau zoo.

Cov Turbines CuaSiv cov thev naus laus zis SiC hauvcov tshuab tswj cua turbine, optimizing lub zog tsim thiab hloov pauv efficiency.

Aerospace thiab Defense:

SiC wafers zoo tagnrho rau kev siv rau hauvkev siv hluav taws xob hauv aerospacethiabdaim ntawv thov tub rog, suav nrogcov txheej txheem radarthiabcov khoom siv hluav taws xob satellite, qhov twg kev tiv taus hluav taws xob siab thiab kev ruaj khov thermal yog qhov tseem ceeb.

Cov Ntawv Thov Kub thiab Zaus Siab:

SiC wafers ua tau zoo heevcov khoom siv hluav taws xob kub siab, siv rau hauvcov cav dav hlau, lub dav hlau, thiabcov tshuab cua sov rau kev lag luam, vim lawv tswj tau qhov ua tau zoo hauv qhov kub heev. Tsis tas li ntawd, lawv qhov bandgap dav dav tso cai rau kev siv hauvcov ntawv thov zaus siabzoo liCov khoom siv RFthiabkev sib txuas lus microwave.

| 6-nti N-hom epit axial specification | |||

| Cov Qauv | chav tsev | Z-MOS | |

| Hom | Kev sib txuas lus / Dopant | - | N-hom / Nitrogen |

| Txheej tsis | Qhov tuab ntawm cov txheej txheem tsis | um | 1 |

| Kev kam rau siab ntawm cov txheej txheem tsis sib xws | % | ±20% | |

| Kev Ntsuas Txheej Buffer | cm-3 | 1.00E+18 | |

| Kev kam rau siab ntawm cov txheej txheem tsis sib xws | % | ±20% | |

| Txheej Epi 1st | Epi Txheej Thickness | um | 11.5 |

| Epi Txheej Thickness Uniformity | % | ±4% | |

| Epi Layers Thickness Tolerance ((Spec- Max, Min) / Spec) | % | ±5% | |

| Epi Txheej Concentration | cm-3 | 1E 15~ 1E 18 | |

| Kev kam rau siab ntawm Epi Txheej | % | 6% | |

| Kev Sib Npaug ntawm Epi Txheej (σ) /txhais tau tias) | % | ≤5% | |

| Epi Txheej Concentration Uniformity <(siab tshaj plaws-qis tshaj plaws)/(siab tshaj plaws+qis tshaj plaws> | % | ≤ 10% | |

| Cov duab ntawm Epitaixal Wafer | Hneev | um | ≤ ± 20 |

| WARP | um | ≤30 | |

| TTV | um | ≤ 10 | |

| LTV | um | ≤2 | |

| Cov Yam Ntxwv Dav Dav | Qhov ntev ntawm qhov khawb | mm | ≤30 hli |

| Cov Chips Ntug | - | TSIS MUAJ | |

| Kev txhais cov teeb meem | ≥97% (Ntsuas nrog 2 * 2, Cov kev tsis zoo uas ua rau tuag taus suav nrog: Cov kev tsis zoo suav nrog Micropipe / Cov qhov loj, Carrot, Triangular | ||

| Kev ua qias tuaj ntawm hlau | atoms/cm² | d f f ll i ≤5E10 atoms / cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca & Mn) | |

| Pob khoom | Cov lus qhia txog kev ntim khoom | ib thooj/lub thawv | ntau lub wafer cassette lossis ib lub thawv wafer |

| 8-nti N-hom epitaxial specification | |||

| Cov Qauv | chav tsev | Z-MOS | |

| Hom | Kev sib txuas lus / Dopant | - | N-hom / Nitrogen |

| Txheej tsis | Qhov tuab ntawm cov txheej txheem tsis | um | 1 |

| Kev kam rau siab ntawm cov txheej txheem tsis sib xws | % | ±20% | |

| Kev Ntsuas Txheej Buffer | cm-3 | 1.00E+18 | |

| Kev kam rau siab ntawm cov txheej txheem tsis sib xws | % | ±20% | |

| Txheej Epi 1st | Qhov Nruab Nrab ntawm Epi Layers Thickness | um | 8~ 12 |

| Epi Layers Thickness Uniformity (σ / nruab nrab) | % | ≤2.0 | |

| Epi Layers Thickness Tolerance ((Spec -Max, Min) / Spec) | % | ±6 | |

| Epi Layers Net Average Doping | cm-3 | 8E+15 ~2E+16 | |

| Epi Layers Net Doping Uniformity (σ / nruab nrab) | % | ≤5 | |

| Epi Layers Net DopingTolerance ((Spec -Max, | % | ± 10.0 | |

| Cov duab ntawm Epitaixal Wafer | Mi )/S ) Ua kom nkhaus | um | ≤50.0 |

| Hneev | um | ± 30.0 | |

| TTV | um | ≤ 10.0 | |

| LTV | um | ≤4.0 (10mm × 10mm) | |

| Dav Dav Cov yam ntxwv | Cov khawb | - | Tag nrho ntev ≤ 1/2 Wafer txoj kab uas hla |

| Cov Chips Ntug | - | ≤2 daim, Txhua lub vojvoog ≤1.5 hli | |

| Kev Ua Phem Rau Cov Hlau Nto | atoms/cm2 | ≤5E10 atoms / cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca & Mn) | |

| Kev Tshuaj Xyuas Qhov Tsis Zoo | % | ≥ 96.0 (2X2 Qhov tsis zoo suav nrog Micropipe / Cov qhov loj, Qos yaj ywm, Cov qhov tsis zoo ntawm daim duab peb ceg, Kev poob qis, Kab ncaj/IGSF-s, BPD) | |

| Kev Ua Phem Rau Cov Hlau Nto | atoms/cm2 | ≤5E10 atoms / cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca & Mn) | |

| Pob khoom | Cov lus qhia txog kev ntim khoom | - | ntau lub wafer cassette lossis ib lub thawv wafer |

Cov Lus Nug thiab Lus Teb ntawm SiC wafer

Q1: Cov txiaj ntsig tseem ceeb ntawm kev siv SiC wafers dua li cov silicon wafers ib txwm muaj hauv cov khoom siv hluav taws xob yog dab tsi?

A1:

SiC wafers muaj ntau qhov zoo dua li cov silicon (Si) wafers ib txwm muaj hauv cov khoom siv hluav taws xob, suav nrog:

Kev Ua Haujlwm Zoo DuaSiC muaj qhov bandgap dav dua (3.26 eV) piv rau silicon (1.1 eV), uas tso cai rau cov khoom siv ua haujlwm ntawm qhov hluav taws xob siab dua, zaus, thiab kub dua. Qhov no ua rau poob hluav taws xob tsawg dua thiab ua haujlwm tau zoo dua hauv cov txheej txheem hloov hluav taws xob.

Kev Ua Haujlwm Thermal SiabSiC lub thermal conductivity siab dua li ntawm silicon, ua rau muaj kev kub hnyiab zoo dua hauv cov ntawv thov fais fab siab, uas ua rau kev ntseeg tau thiab lub neej ntawm cov khoom siv fais fab zoo dua.

Kev Tswj Xyuas Voltage Thiab Tam Sim No Siab DuaCov khoom siv SiC tuaj yeem tswj tau cov hluav taws xob thiab cov hluav taws xob siab dua, ua rau lawv tsim nyog rau cov ntawv thov muaj zog xws li tsheb fais fab, cov tshuab hluav taws xob rov ua dua tshiab, thiab cov tsav tsheb hauv kev lag luam.

Kev Hloov Ceev Sai Dua: Cov khoom siv SiC muaj peev xwm hloov pauv sai dua, uas pab txo qhov kev poob zog thiab qhov loj ntawm lub kaw lus, ua rau lawv zoo tagnrho rau cov ntawv thov zaus siab.

Q2: Cov ntawv thov tseem ceeb ntawm SiC wafers hauv kev lag luam tsheb yog dab tsi?

A2:

Hauv kev lag luam tsheb, SiC wafers feem ntau yog siv rau hauv:

Lub Tsheb Fais Fab (EV) Lub Cev Muaj ZogCov khoom siv SiC zoo licov invertersthiabMOSFETs fais fabtxhim kho qhov ua tau zoo thiab kev ua tau zoo ntawm cov tsheb fais fab los ntawm kev ua kom muaj kev hloov pauv sai dua thiab muaj zog ntau dua. Qhov no ua rau lub roj teeb siv tau ntev dua thiab kev ua tau zoo ntawm lub tsheb zoo dua.

Cov Khoom Siv Hluav Taws Xob Hauv TsevCov khoom siv SiC pab txhim kho kev ua haujlwm ntawm cov tshuab them hluav taws xob hauv tsheb los ntawm kev ua kom lub sijhawm them sai dua thiab kev tswj hwm cua sov zoo dua, uas yog qhov tseem ceeb rau EVs los txhawb cov chaw them hluav taws xob muaj zog siab.

Cov Txheej Txheem Tswj Xyuas Roj Teeb (BMS): SiC thev naus laus zis txhim kho kev ua haujlwm ntawmcov txheej txheem tswj roj teeb, uas ua rau muaj kev tswj hwm hluav taws xob zoo dua, kev tswj hwm hluav taws xob zoo dua, thiab lub roj teeb siv tau ntev dua.

Cov Hloov DC-DCSiC wafers siv rau hauvCov hloov pauv DC-DClos hloov lub zog DC siab mus rau lub zog DC qis kom zoo dua, uas yog qhov tseem ceeb hauv cov tsheb fais fab kom tswj tau lub zog los ntawm lub roj teeb mus rau ntau yam khoom hauv lub tsheb.

SiC qhov kev ua tau zoo tshaj plaws hauv kev siv hluav taws xob siab, kub siab, thiab kev siv ua haujlwm tau zoo ua rau nws tseem ceeb rau kev hloov pauv ntawm kev lag luam tsheb mus rau kev siv hluav taws xob.

6 nti 4H-N hom SiC wafer cov lus qhia tshwj xeeb | ||

| Vaj tse | Qib Tsim Khoom Xoom MPD (Qib Z) | Qib Dummy (Qib D) |

| Qib | Qib Tsim Khoom Xoom MPD (Qib Z) | Qib Dummy (Qib D) |

| Txoj kab uas hla | 149.5 hli - 150.0 hli | 149.5 hli - 150.0 hli |

| Poly-hom | 4H | 4H |

| Qhov tuab | 350 µm ± 15 µm | 350 µm ± 25 µm |

| Kev Taw Qhia Wafer | Tawm ntawm txoj kab: 4.0° mus rau <1120> ± 0.5° | Tawm ntawm txoj kab: 4.0° mus rau <1120> ± 0.5° |

| Qhov Ceev ntawm Micropipe | ≤ 0.2 cm² | ≤ 15 cm² |

| Kev tiv taus | 0.015 – 0.024 Ω·cm | 0.015 – 0.028 Ω·cm |

| Kev Taw Qhia Tiaj Tus Thawj Coj | [10-10] ± 50° | [10-10] ± 50° |

| Qhov Ntev Tiaj Tus Thawj | 475 hli ± 2.0 hli | 475 hli ± 2.0 hli |

| Kev Tshem Tawm Ntug | 3 hli | 3 hli |

| LTV/TIV / Bow / Warp | ≤ 2.5 µm / ≤ 6 µm / ≤ 25 µm / ≤ 35 µm | ≤ 5 µm / ≤ 15 µm / ≤ 40 µm / ≤ 60 µm |

| Kev ntxhib | Polish Ra ≤ 1 nm | Polish Ra ≤ 1 nm |

| CMP Ra | ≤ 0.2 nm | ≤ 0.5 nm |

| Cov Ntxaij Ntug Los Ntawm Lub Teeb Ci Siab | Qhov ntev tag nrho ≤ 20 hli ib qho ntev ≤ 2 hli | Qhov ntev tag nrho ≤ 20 hli ib qho ntev ≤ 2 hli |

| Hex Phaj Los Ntawm Lub Teeb Ci Siab | Thaj chaw sib sau ua ke ≤ 0.05% | Thaj chaw sib sau ua ke ≤ 0.1% |

| Cov Cheeb Tsam Polytype Los Ntawm Lub Teeb Ci Siab | Thaj chaw sib sau ua ke ≤ 0.05% | Thaj chaw sib sau ua ke ≤ 3% |

| Cov pa roj carbon uas pom tau | Thaj chaw sib sau ua ke ≤ 0.05% | Thaj chaw sib sau ua ke ≤ 5% |

| Cov khawb ntawm cov nplaim silicon los ntawm lub teeb ci ntsa iab | Qhov ntev tag nrho ≤ 1 lub wafer txoj kab uas hla | |

| Ntug Chips Los Ntawm Lub Teeb Ci Siab | Tsis pub muaj ≥ 0.2 hli dav thiab tob | 7 tso cai, ≤ 1 hli txhua |

| Kev Sib Tsoo Ntawm Cov Ntsia Hlau | < 500 cm³ | < 500 cm³ |

| Kev Ua Rau Silicon Nto Los Ntawm Lub Teeb Ci Siab | ||

| Ntim Khoom | Multi-wafer Cassette Los Yog Ib Lub Thawv Wafer | Multi-wafer Cassette Los Yog Ib Lub Thawv Wafer |

8 nti 4H-N hom SiC wafer cov lus qhia tshwj xeeb | ||

| Vaj tse | Qib Tsim Khoom Xoom MPD (Qib Z) | Qib Dummy (Qib D) |

| Qib | Qib Tsim Khoom Xoom MPD (Qib Z) | Qib Dummy (Qib D) |

| Txoj kab uas hla | 199.5 hli - 200.0 hli | 199.5 hli - 200.0 hli |

| Poly-hom | 4H | 4H |

| Qhov tuab | 500 µm ± 25 µm | 500 µm ± 25 µm |

| Kev Taw Qhia Wafer | 4.0° mus rau <110> ± 0.5° | 4.0° mus rau <110> ± 0.5° |

| Qhov Ceev ntawm Micropipe | ≤ 0.2 cm² | ≤ 5 cm² |

| Kev tiv taus | 0.015 – 0.025 Ω·cm | 0.015 – 0.028 Ω·cm |

| Kev Taw Qhia Zoo | ||

| Kev Tshem Tawm Ntug | 3 hli | 3 hli |

| LTV/TIV / Bow / Warp | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 70 µm | ≤ 5 µm / ≤ 15 µm / ≤ 35 µm / 100 µm |

| Kev ntxhib | Polish Ra ≤ 1 nm | Polish Ra ≤ 1 nm |

| CMP Ra | ≤ 0.2 nm | ≤ 0.5 nm |

| Cov Ntxaij Ntug Los Ntawm Lub Teeb Ci Siab | Qhov ntev tag nrho ≤ 20 hli ib qho ntev ≤ 2 hli | Qhov ntev tag nrho ≤ 20 hli ib qho ntev ≤ 2 hli |

| Hex Phaj Los Ntawm Lub Teeb Ci Siab | Thaj chaw sib sau ua ke ≤ 0.05% | Thaj chaw sib sau ua ke ≤ 0.1% |

| Cov Cheeb Tsam Polytype Los Ntawm Lub Teeb Ci Siab | Thaj chaw sib sau ua ke ≤ 0.05% | Thaj chaw sib sau ua ke ≤ 3% |

| Cov pa roj carbon uas pom tau | Thaj chaw sib sau ua ke ≤ 0.05% | Thaj chaw sib sau ua ke ≤ 5% |

| Cov khawb ntawm cov nplaim silicon los ntawm lub teeb ci ntsa iab | Qhov ntev tag nrho ≤ 1 lub wafer txoj kab uas hla | |

| Ntug Chips Los Ntawm Lub Teeb Ci Siab | Tsis pub muaj ≥ 0.2 hli dav thiab tob | 7 tso cai, ≤ 1 hli txhua |

| Kev Sib Tsoo Ntawm Cov Ntsia Hlau | < 500 cm³ | < 500 cm³ |

| Kev Ua Rau Silicon Nto Los Ntawm Lub Teeb Ci Siab | ||

| Ntim Khoom | Multi-wafer Cassette Los Yog Ib Lub Thawv Wafer | Multi-wafer Cassette Los Yog Ib Lub Thawv Wafer |

6Inch 4H-semi SiC substrate specification | ||

| Vaj tse | Qib Tsim Khoom Xoom MPD (Qib Z) | Qib Dummy (Qib D) |

| Txoj kab uas hla (hli) | 145 hli - 150 hli | 145 hli - 150 hli |

| Poly-hom | 4H | 4H |

| Thickness (um) | 500 ± 15 | 500 ± 25 |

| Kev Taw Qhia Wafer | Nyob rau ntawm axis: ± 0.0001 ° | Ntawm axis: ±0.05° |

| Qhov Ceev ntawm Micropipe | ≤ 15 cm-2 | ≤ 15 cm-2 |

| Kev tiv thaiv (Ωcm) | ≥ 10E3 | ≥ 10E3 |

| Kev Taw Qhia Tiaj Tus Thawj Coj | (0-10)° ± 5.0° | (10-10)° ± 5.0° |

| Qhov Ntev Tiaj Tus Thawj | Qhov Notch | Qhov Notch |

| Kev Tshem Tawm Ntug (hli) | ≤ 2.5 µm / ≤ 15 µm | ≤ 5.5 µm / ≤ 35 µm |

| LTV / Bowl / Warp | ≤ 3 µm | ≤ 3 µm |

| Kev ntxhib | Polish Ra ≤ 1.5 µm | Polish Ra ≤ 1.5 µm |

| Ntug Chips Los Ntawm Lub Teeb Ci Siab | ≤ 20 µm | ≤ 60 µm |

| Cov Phaj Kub Los Ntawm Lub Teeb Ci Siab | Tag nrho ≤ 0.05% | Tag nrho ≤ 3% |

| Cov Cheeb Tsam Polytype Los Ntawm Lub Teeb Ci Siab | Cov Pa roj carbon uas pom tau ≤ 0.05% | Tag nrho ≤ 3% |

| Cov khawb ntawm cov nplaim silicon los ntawm lub teeb ci ntsa iab | ≤ 0.05% | Tag nrho ≤ 4% |

| Cov Chips Ntug Los Ntawm Lub Teeb Ci Siab (Qhov Loj) | Tsis Pub > 02 hli Dav thiab Qhov Tob | Tsis Pub > 02 hli Dav thiab Qhov Tob |

| Kev Pab Txhawb Nqa Kev Nthuav Dav | ≤ 500 µm | ≤ 500 µm |

| Kev Ua Rau Silicon Nto Los Ntawm Lub Teeb Ci Siab | ≤ 1 x 10^5 | ≤ 1 x 10^5 |

| Ntim Khoom | Multi-wafer Cassette los yog Single Wafer Thawv | Multi-wafer Cassette los yog Single Wafer Thawv |

Cov Lus Qhia Txog 4-Nti 4H-Semi Insulating SiC Substrate

| Cov Qauv | Qib Tsim Khoom Xoom MPD (Qib Z) | Qib Dummy (Qib D) |

|---|---|---|

| Cov Khoom Siv Lub Cev | ||

| Txoj kab uas hla | 99.5 hli - 100.0 hli | 99.5 hli - 100.0 hli |

| Poly-hom | 4H | 4H |

| Qhov tuab | 500 μm ± 15 μm | 500 μm ± 25 μm |

| Kev Taw Qhia Wafer | Nyob rau ntawm axis: <600h> 0.5° | Nyob rau ntawm axis: <000h> 0.5 ° |

| Cov Khoom Siv Hluav Taws Xob | ||

| Qhov Ceev ntawm Cov Kav Dej Me Me (MPD) | ≤1 cm⁻² | ≤15 cm⁻² |

| Kev tiv taus | ≥150 Ω·cm | ≥1.5 Ω·cm |

| Kev kam rau siab geometric | ||

| Kev Taw Qhia Tiaj Tus Thawj Coj | (0 × 10) ± 5.0 ° | (0 × 10) ± 5.0 ° |

| Qhov Ntev Tiaj Tus Thawj | 52.5 hli ± 2.0 hli | 52.5 hli ± 2.0 hli |

| Qhov Ntev Thib Ob | 18.0 hli ± 2.0 hli | 18.0 hli ± 2.0 hli |

| Kev Taw Qhia Qib Thib Ob | 90° CW ntawm Prime tiaj tus ± 5.0° (Si ntsej muag rau saum) | 90° CW ntawm Prime tiaj tus ± 5.0° (Si ntsej muag rau saum) |

| Kev Tshem Tawm Ntug | 3 hli | 3 hli |

| LTV / TTV / Bow / Warp | ≤2.5 μm / ≤5 μm / ≤15 μm / ≤30 μm | ≤10μm / ≤15μm / ≤25μm / ≤40μm |

| Qhov Zoo Ntawm Qhov Chaw | ||

| Qhov Roughness ntawm qhov chaw (Polish Ra) | ≤1 nm | ≤1 nm |

| Qhov Roughness ntawm Qhov Chaw (CMP Ra) | ≤0.2 nm | ≤0.2 nm |

| Cov Ntxaij Ntug (Lub Teeb Ci Muaj Zog) | Tsis pub | Qhov ntev sib sau ua ke ≥10 hli, ib qho tawg ≤2 hli |

| Cov Teeb Meem Phaj Hexagonal | ≤0.05% thaj chaw sib sau ua ke | ≤0.1% thaj chaw sib sau ua ke |

| Cov Cheeb Tsam suav nrog Polytype | Tsis pub | ≤1% thaj chaw sib sau ua ke |

| Cov pa roj carbon uas pom tau | ≤0.05% thaj chaw sib sau ua ke | ≤1% thaj chaw sib sau ua ke |

| Cov khawb ntawm qhov chaw silicon | Tsis pub | ≤1 wafer txoj kab uas hla cumulative ntev |

| Cov Chips Ntug | Tsis pub muaj (≥0.2 hli dav/qhov tob) | ≤5 daim (txhua ≤1 hli) |

| Kev Ua Phem Rau Qhov Chaw Silicon | Tsis tau teev tseg | Tsis tau teev tseg |

| Ntim Khoom | ||

| Ntim Khoom | Lub thawv ntim ntau lub wafer los yog lub thawv ntim ib lub wafer | Cov cassette ntau lub wafer los yog |

| 6-nti N-hom epit axial specification | |||

| Cov Qauv | chav tsev | Z-MOS | |

| Hom | Kev sib txuas lus / Dopant | - | N-hom / Nitrogen |

| Txheej tsis | Qhov tuab ntawm cov txheej txheem tsis | um | 1 |

| Kev kam rau siab ntawm cov txheej txheem tsis sib xws | % | ±20% | |

| Kev Ntsuas Txheej Buffer | cm-3 | 1.00E+18 | |

| Kev kam rau siab ntawm cov txheej txheem tsis sib xws | % | ±20% | |

| Txheej Epi 1st | Epi Txheej Thickness | um | 11.5 |

| Epi Txheej Thickness Uniformity | % | ±4% | |

| Epi Layers Thickness Tolerance ((Spec- Max, Min) / Spec) | % | ±5% | |

| Epi Txheej Concentration | cm-3 | 1E 15~ 1E 18 | |

| Kev kam rau siab ntawm Epi Txheej | % | 6% | |

| Kev Sib Npaug ntawm Epi Txheej (σ) /txhais tau tias) | % | ≤5% | |

| Epi Txheej Concentration Uniformity <(siab tshaj plaws-qis tshaj plaws)/(siab tshaj plaws+qis tshaj plaws> | % | ≤ 10% | |

| Cov duab ntawm Epitaixal Wafer | Hneev | um | ≤ ± 20 |

| WARP | um | ≤30 | |

| TTV | um | ≤ 10 | |

| LTV | um | ≤2 | |

| Cov Yam Ntxwv Dav Dav | Qhov ntev ntawm qhov khawb | mm | ≤30 hli |

| Cov Chips Ntug | - | TSIS MUAJ | |

| Kev txhais cov teeb meem | ≥97% (Ntsuas nrog 2 * 2, Cov kev tsis zoo uas ua rau tuag taus suav nrog: Cov kev tsis zoo suav nrog Micropipe / Cov qhov loj, Carrot, Triangular | ||

| Kev ua qias tuaj ntawm hlau | atoms/cm² | d f f ll i ≤5E10 atoms / cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca & Mn) | |

| Pob khoom | Cov lus qhia txog kev ntim khoom | ib thooj/lub thawv | ntau lub wafer cassette lossis ib lub thawv wafer |

| 8-nti N-hom epitaxial specification | |||

| Cov Qauv | chav tsev | Z-MOS | |

| Hom | Kev sib txuas lus / Dopant | - | N-hom / Nitrogen |

| Txheej tsis | Qhov tuab ntawm cov txheej txheem tsis | um | 1 |

| Kev kam rau siab ntawm cov txheej txheem tsis sib xws | % | ±20% | |

| Kev Ntsuas Txheej Buffer | cm-3 | 1.00E+18 | |

| Kev kam rau siab ntawm cov txheej txheem tsis sib xws | % | ±20% | |

| Txheej Epi 1st | Qhov Nruab Nrab ntawm Epi Layers Thickness | um | 8~ 12 |

| Epi Layers Thickness Uniformity (σ / nruab nrab) | % | ≤2.0 | |

| Epi Layers Thickness Tolerance ((Spec -Max, Min) / Spec) | % | ±6 | |

| Epi Layers Net Average Doping | cm-3 | 8E+15 ~2E+16 | |

| Epi Layers Net Doping Uniformity (σ / nruab nrab) | % | ≤5 | |

| Epi Layers Net DopingTolerance ((Spec -Max, | % | ± 10.0 | |

| Cov duab ntawm Epitaixal Wafer | Mi )/S ) Ua kom nkhaus | um | ≤50.0 |

| Hneev | um | ± 30.0 | |

| TTV | um | ≤ 10.0 | |

| LTV | um | ≤4.0 (10mm × 10mm) | |

| Dav Dav Cov yam ntxwv | Cov khawb | - | Tag nrho ntev ≤ 1/2 Wafer txoj kab uas hla |

| Cov Chips Ntug | - | ≤2 daim, Txhua lub vojvoog ≤1.5 hli | |

| Kev Ua Phem Rau Cov Hlau Nto | atoms/cm2 | ≤5E10 atoms / cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca & Mn) | |

| Kev Tshuaj Xyuas Qhov Tsis Zoo | % | ≥ 96.0 (2X2 Qhov tsis zoo suav nrog Micropipe / Cov qhov loj, Qos yaj ywm, Cov qhov tsis zoo ntawm daim duab peb ceg, Kev poob qis, Kab ncaj/IGSF-s, BPD) | |

| Kev Ua Phem Rau Cov Hlau Nto | atoms/cm2 | ≤5E10 atoms / cm2 (Al, Cr, Fe, Ni, Cu, Zn, Hg, Na, K, Ti, Ca & Mn) | |

| Pob khoom | Cov lus qhia txog kev ntim khoom | - | ntau lub wafer cassette lossis ib lub thawv wafer |

Q1: Cov txiaj ntsig tseem ceeb ntawm kev siv SiC wafers dua li cov silicon wafers ib txwm muaj hauv cov khoom siv hluav taws xob yog dab tsi?

A1:

SiC wafers muaj ntau qhov zoo dua li cov silicon (Si) wafers ib txwm muaj hauv cov khoom siv hluav taws xob, suav nrog:

Kev Ua Haujlwm Zoo DuaSiC muaj qhov bandgap dav dua (3.26 eV) piv rau silicon (1.1 eV), uas tso cai rau cov khoom siv ua haujlwm ntawm qhov hluav taws xob siab dua, zaus, thiab kub dua. Qhov no ua rau poob hluav taws xob tsawg dua thiab ua haujlwm tau zoo dua hauv cov txheej txheem hloov hluav taws xob.

Kev Ua Haujlwm Thermal SiabSiC lub thermal conductivity siab dua li ntawm silicon, ua rau muaj kev kub hnyiab zoo dua hauv cov ntawv thov fais fab siab, uas ua rau kev ntseeg tau thiab lub neej ntawm cov khoom siv fais fab zoo dua.

Kev Tswj Xyuas Voltage Thiab Tam Sim No Siab DuaCov khoom siv SiC tuaj yeem tswj tau cov hluav taws xob thiab cov hluav taws xob siab dua, ua rau lawv tsim nyog rau cov ntawv thov muaj zog xws li tsheb fais fab, cov tshuab hluav taws xob rov ua dua tshiab, thiab cov tsav tsheb hauv kev lag luam.

Kev Hloov Ceev Sai Dua: Cov khoom siv SiC muaj peev xwm hloov pauv sai dua, uas pab txo qhov kev poob zog thiab qhov loj ntawm lub kaw lus, ua rau lawv zoo tagnrho rau cov ntawv thov zaus siab.

Q2: Cov ntawv thov tseem ceeb ntawm SiC wafers hauv kev lag luam tsheb yog dab tsi?

A2:

Hauv kev lag luam tsheb, SiC wafers feem ntau yog siv rau hauv:

Lub Tsheb Fais Fab (EV) Lub Cev Muaj ZogCov khoom siv SiC zoo licov invertersthiabMOSFETs fais fabtxhim kho qhov ua tau zoo thiab kev ua tau zoo ntawm cov tsheb fais fab los ntawm kev ua kom muaj kev hloov pauv sai dua thiab muaj zog ntau dua. Qhov no ua rau lub roj teeb siv tau ntev dua thiab kev ua tau zoo ntawm lub tsheb zoo dua.

Cov Khoom Siv Hluav Taws Xob Hauv TsevCov khoom siv SiC pab txhim kho kev ua haujlwm ntawm cov tshuab them hluav taws xob hauv tsheb los ntawm kev ua kom lub sijhawm them sai dua thiab kev tswj hwm cua sov zoo dua, uas yog qhov tseem ceeb rau EVs los txhawb cov chaw them hluav taws xob muaj zog siab.

Cov Txheej Txheem Tswj Xyuas Roj Teeb (BMS): SiC thev naus laus zis txhim kho kev ua haujlwm ntawmcov txheej txheem tswj roj teeb, uas ua rau muaj kev tswj hwm hluav taws xob zoo dua, kev tswj hwm hluav taws xob zoo dua, thiab lub roj teeb siv tau ntev dua.

Cov Hloov DC-DCSiC wafers siv rau hauvCov hloov pauv DC-DClos hloov lub zog DC siab mus rau lub zog DC qis kom zoo dua, uas yog qhov tseem ceeb hauv cov tsheb fais fab kom tswj tau lub zog los ntawm lub roj teeb mus rau ntau yam khoom hauv lub tsheb.

SiC qhov kev ua tau zoo tshaj plaws hauv kev siv hluav taws xob siab, kub siab, thiab kev siv ua haujlwm tau zoo ua rau nws tseem ceeb rau kev hloov pauv ntawm kev lag luam tsheb mus rau kev siv hluav taws xob.